Регистр VPBDIV (VPBDIV-OxEOIFCWO)

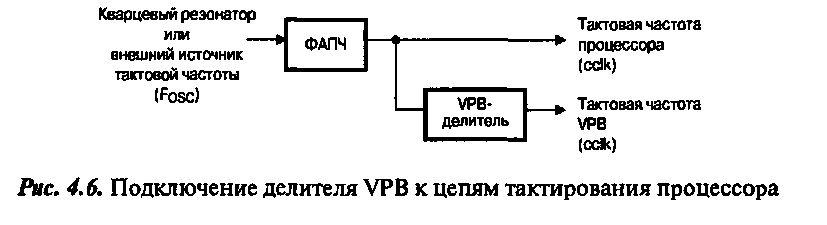

Описание регистра VPBDIV приведено в Табл. 4.23. Битовая структура регистра VPBDIV приведена в Табл. 4.24. Регистр делителя VPB содержит два бита и позволяет задать три значения коэффициента деления, приведенные в Табл. 4.24.

Таблица 4.23. Регистр делителя VPB VPBDIV

|

Адрес |

Название |

Описание |

Доступ |

|

OxEOlFClOO |

VPBDIV |

Управляет значением тактовой частоты VPB, задаваемой относительно тактовой частоты процессора (cclk) |

R/W |

Таблица 4.24. Биты регистра делителя VPB (VPBDIV — OxEOlFClOO)

|

Номер бита |

Название бита |

Функция бита |

Значение после сброса |

|

1:0 |

VPBDIV |

В зависимости от состояния этих двух битов, частота синхросигнала VPB может принимать следующие значения: 00: Частота VPB равна 1/4 частоты тактового сигнала процессора. 01: Частота VPB равна частоте тактового сигнала процессора. 10: Частота VPB равна 1/2 частоты тактового сигнала процессора. 11: Зарезервировано. Запись этого значения в регистр VPBDIV не производится (т. е. сохраняется текущее значение битов VPBDIV) |

0 |

|

3:2 |

Зарезервированы |

Пользовательское программное обеспечение не должно производить запись в зарезервированные биты. Чтение зарезервированного бита возвращает неопределенное значение |

0 |

Таблица 4.24. Биты регистра делителя VPB (VPBDIV — OxEOlFClOO) (продолжение)

|

Номер бита |

Название бита |

Функция бита |

Значение после сброса |

|

5:4 |

XCLKDIV |

В микроконтроллерах LPC2000 с 144-выводным корпусом эти биты управляют синхросигналом, который формируется внутренний логической схемой микроконтроллера и может подаваться на вывод A23/XCLK. В зависимости от состояния этих двух битов, частота синхросигнала может принимать следующие значения: 00: Частота XCLK равна 1/4 частоты тактового сигнала процессора. 01: Частота XCLK равна частоте тактового сигнала процессора. 10: Частота XCLK равна 1/2 частоты тактового сигнала процессора. 11: Зарезервировано. Запись этого значения в регистр VPB DIV не производится (т. е. сохраняется текущее значение битов XCLKDIV). Рабочая в данный момент функция вывода A23/XCLK определяется состоянием соответствующего бита регистра PINSEL2 (см. главу 8«Блок коммутации выводов»). Примечание. Если значения битов XCLKDIV и VPBDIV совпадают друг с другом, то один и тот же синхросигнал используется для VPB и XCLK. (Это может быть полезно для внешней логики, взаимодействующей с периферийными устройствами VPB.) |

0 |

|

7:6 |

Зарезервированы |

Пользовательское программное обеспечение не должно производить запись в зарезервированные биты. Чтение зарезервированного бита возвращает неопределенное значение |

0 |

4.11. Таймер «пробуждения»

Назначение таймера «пробуждения» состоит в том, чтобы гарантировать, что тактовый генератор и другие необходимые для осуществления внутренних операций микроконтроллера встроенные аналоговые схемы полностью выйдут на свои рабочие режимы прежде, чем процессору будет разрешено выполнять команды. Таймер «пробуждения» используется в следующих случаях: при включении питания микроконтроллера, при любом сбросе, а также после отключения (по той или иной причине) любой из вышеупомянутых аналоговых схем. Таймер «пробуждения» используется также при любом «пробуждении» микроконтроллера из режима Power Down, так как в этом режиме генератор и другие функции отключены.

| НА ГЛАВНУЮ | | ЧТО ТАКОЕ PIC ? | | ПРОГРАММАТОР | | ПРОЕКТЫ | | СТАТЬИ | | ССЫЛКИ | | КАРТА САЙТА |