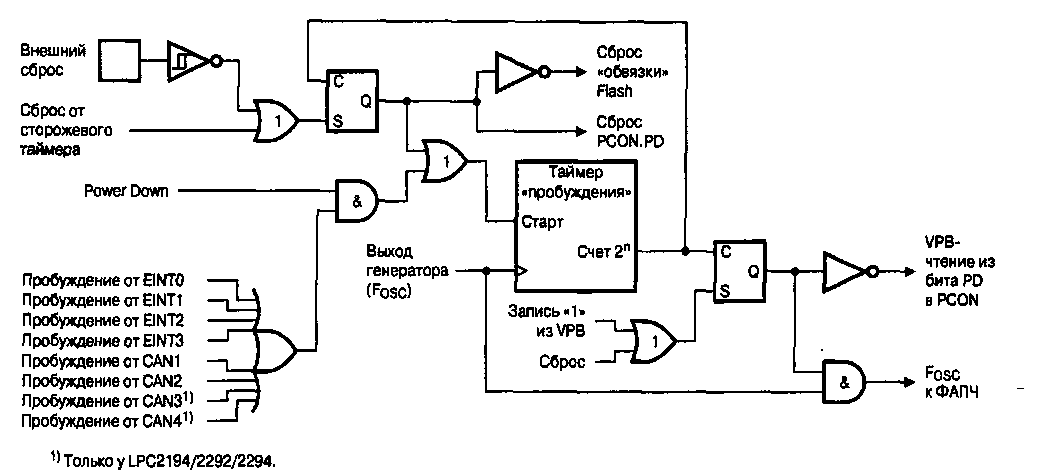

Рис. 4.5. Функциональная схема внутренней логики сброса (на примере микроконтроллеров

LPC2119/29/94 и LPC2292/94)

После завершения процедуры внутреннего сброса, процессор микроконтроллера приступает к выполнению программы с адреса 0, на который отображен вектор сброса в загрузочном блоке. В этот момент сам процессор и периферийные регистры инициализируются заданными (установленными по умолчанию) значениями.

Процедуры внешнего и внутреннего сброса имеют небольшие различия. При внешнем сбросе функции некоторых выводов автоматически переконфигурируются. При внутреннем сбросе этого не происходит, т.к. внешние цепи микроконтроллера, отвечающие за сброс, не могут отслеживать наступления состояния сброса и производить в этот момент переконфигурирование функций выводов. При внешнем сбросе подвергаются переконфигурированию для различных целей следующие выводы: P1.20/TRACESYNC, P1.26/RTCK, ВООТ1 и ВООТО (см. главу 7 «Цоколевка и назначение выводов», главу 8 «Блок коммутации выводов» и главу 3 «Контроллер внешней памяти»). Вывод Р0.14 (см. главу 20 «Организация и программирование Flash-памяти») используется для нужд встроенного загрузчика при выполнении программного кода после завершения сброса.

Поскольку сброс микроконтроллера, как правило, происходит случайным по времени образом, то возможно наступление сброса во время осуществления операций программирования или стирания встроенной Flash-памяти. В этом случае, контроллер Flash-памяти прервет указанные операции, и будет удерживать центральный процессор в состоянии сброса до тех пор, пока внутренние высокие напряжения программирования не будут сняты.

4.10. Делитель VPB

Делитель VPB служит для того, чтобы задавать соотношение между тактовой частотой процессора (cclk) и частотой, используемой для тактирования периферийных устройства (pclk).

Использование в микроконтроллере LPC2000 делителя VPB преследует две цели. Первая состоит в том, чтобы обеспечить периферийные устройства через шину VPB синхросигналом pclk такой частоты, чтобы они могли работать на

выбранной для процессора ARM скорости. Чтобы достигнуть этого, частота синхросигнала на шине VPB может быть снижена до значения 1/2 или 1/4 тактовой частоты процессора. Значение частоты синхросигнала шины VPB после сброса микроконтроллера составляет 1/4 тактовой частоты процессора (задано по умолчанию) и может быть затем изменено только через регистры управления VPB. Таким образом, гарантируется устойчивая работа шины VPB сразу при включении питания микроконтроллера.

Вторая цель состоит в том, чтобы обеспечить возможность экономии потребляемой мощности микроконтроллера, когда пользовательское приложение не предусматривает использования периферийных устройств, работающих на полной тактовой частоте процессора.

Подключение делителя VPB к генератору и цепям тактирования процессора показано на Рис. 4.6. Поскольку делитель VPB связан с выходом системы ФАПЧ, то система ФАПЧ должна оставаться активной (если она вообще используется) во время действия режима Idle mode.

| НА ГЛАВНУЮ | | ЧТО ТАКОЕ PIC ? | | ПРОГРАММАТОР | | ПРОЕКТЫ | | СТАТЬИ | | ССЫЛКИ | | КАРТА САЙТА |