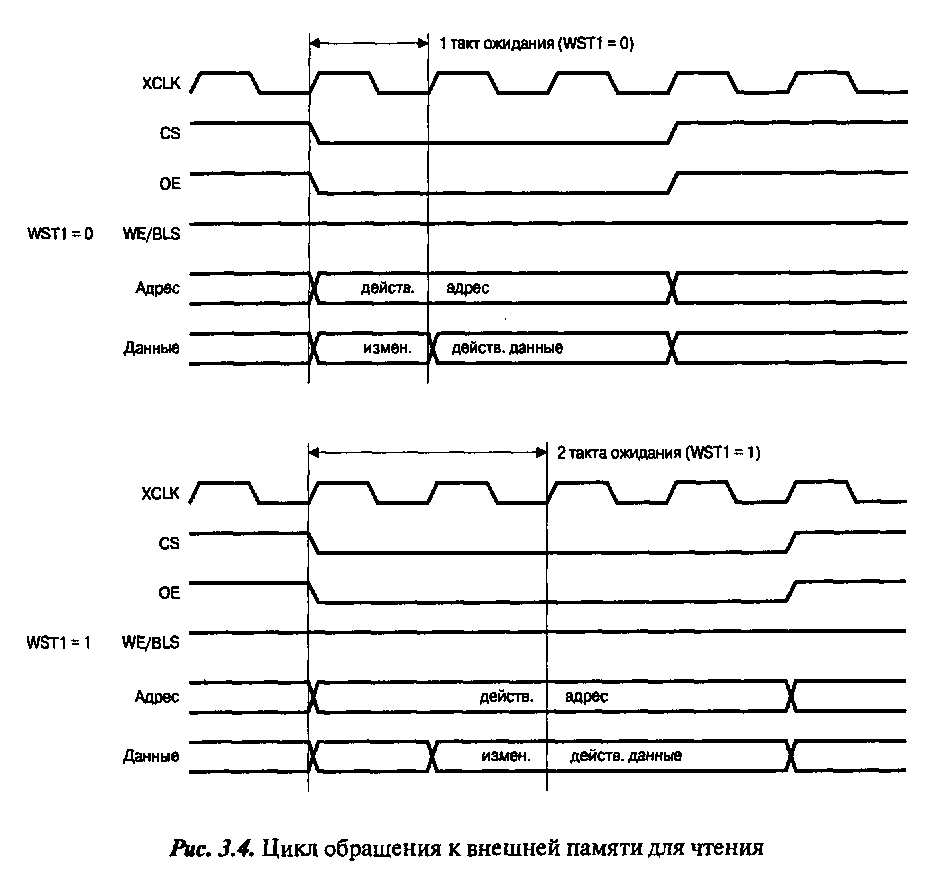

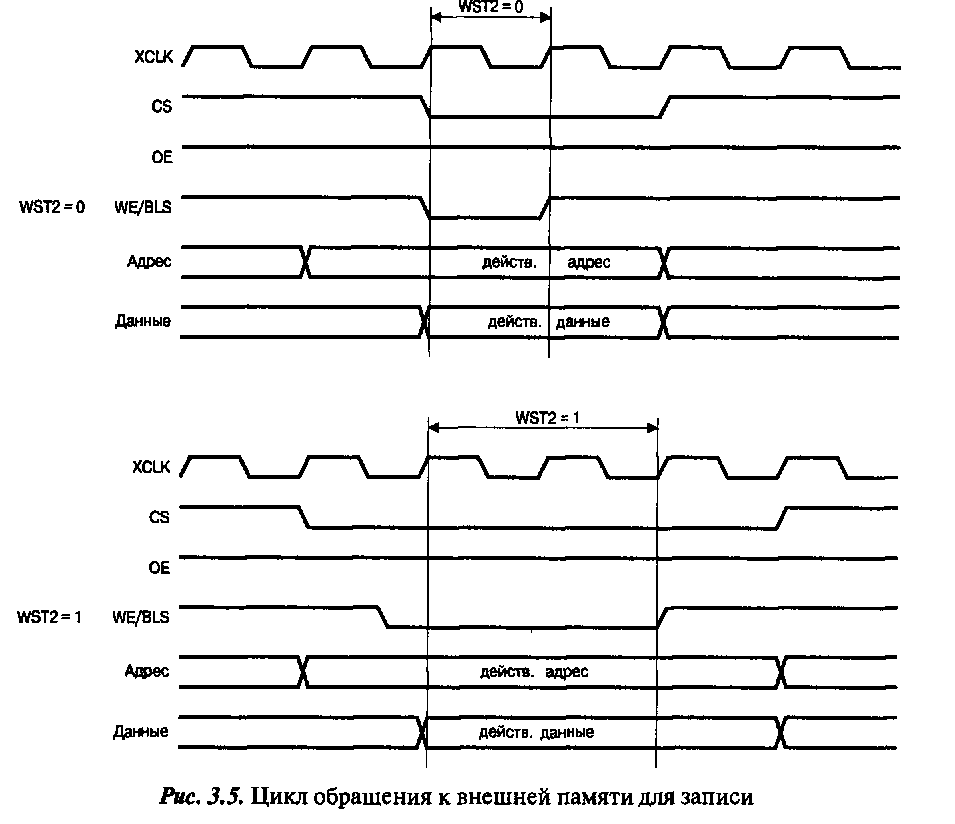

В некоторых специфических случаях вид сигналов на шине внешней памяти может отличаться от диаграмм, изображенных на рисунках. Например, когда выполняется первое обращение для чтения к банку памяти, который был только что выбран, НИЗКИЙ уровень на линиях CS и ОЕ может появиться раньше по времени относительно сигнала XCLK, чем изображено на Рис. 3.4. Аналогично, в последовательности нескольких идущих подряд обращений для записи в SRAM последнее обращение для записи будет выглядеть несколько иначе, чем изображено на Рис. 3.5. Для корректной записи в этом случае потребуется удерживать данные на шине данных на один тактовый цикл дольше. Остальные циклы обращения к памяти для записи не отличаются от изображенного на Рис. 3.5.

3.6. Выбор внешней памяти

В Табл. 3.6 приведены критерии выбора устройств (микросхем) внешней памяти, основанные на приведенном выше описании контроллера внешней памяти и типовых параметрах этих микросхем. В таблице: /ram и /write — интервалы обращения к микросхемам внешней памяти для чтения и для записи, соответственно; /cyc — длительность одного периода сигнала XCLK (см. Рис. 3.4, Рис. 3.5); /„их — максимальная частота CCLK, достижимая в системе с выбранной внешней памятью.

Таблица 3.6. Системные требования к внешней памяти микроконтроллеров семейства LPC2000

|

Тип цикла доступа |

Максимальная частота |

Установка WST (если WST > 0, следует округлить до целого числа) |

Требуемое время доступа памяти |

|

Стандартное чтение |

, _ 2 + WST1 Imax - . , лп „г ram + zu нс |

wst1>'ram + 20hc 2 'cYC |

'ram ^'cyc-(2 + WST1) - 20 нс |

|

Стандартная запись |

, „ 1+WST2 /max - f i с up 'ram + 3 нс |

Wo-p ^ 'write _ 'SYS + 5нс 'cYC |

'write S fcYc'O + WST2) - 5 нс |

БЛОК УПРАВЛЕНИЯ СИСТЕМОЙ

4.1. Основные функции

Блок управления системой микроконтроллеров семейства LPC2000 включает в себя несколько аппаратных узлов и регистров управления множеством независимых друг от друга функций, связанных с определенными периферийными устройствами. (Под функцией понимается реализация какой-либо отдельной задачи, связанной с организацией работы того или иного узла периферии микроконтроллера.)

Блок управления системой включает в себя:

• генератор, стабилизированный кварцевым резонатором;

• входы внешних прерываний;

• узел управления памятью;

• узел ФАПЧ (PLL);

• узел управления потребляемой мощностью;

• узел сброса;

• VPB-делитель;

• таймер «пробуждения» из «спящего» режима.

Каждая функция (узел) имеет свои собственные регистры, если они требуются для контроля и управления, а неиспользуемые в них биты определены как зарезервированные, с учетом последующего их использования в перспективных устройствах. Различные функции никогда не используют совместно регистры с одинаковыми адресами.

4.2. Линии интерфейса управления

В Табл. 4.1 дано описание тех выводов микроконтроллеров семейства LPC2000, которые связаны с блоком управления системой.

| НА ГЛАВНУЮ | | ЧТО ТАКОЕ PIC ? | | ПРОГРАММАТОР | | ПРОЕКТЫ | | СТАТЬИ | | ССЫЛКИ | | КАРТА САЙТА |