• количество неактивных тактовых циклов, вставленных между обращением для чтения и обращением для записи в данном банке, а также между обращениями в данный и в другой банки, чтобы избежать конфликтной ситуации между устройствами памяти при обращении кшине(1...17 тактов);

• длительность обращения для чтения, если последует чтение burst-ROM (3...35 тактов);

• длительность обращения для записи (3... 19 тактов);

• наличие защиты от записи;

• организацию банка памяти (по 8,16 или 32 бита).

В Табл. 3.5 приведено состояние битов BCFG0[29:28] (MW) после того, как запускается загрузчик. Аппаратное состояние этих битов по умолчанию после сброса (без запуска загрузчика) равно 1:0.

Таблица 3.5. Заданная после сброса по умолчанию разрядность внешней памяти LPC2000

|

Банк |

Значения ВООТ[1:0] во время сброса |

Значения BCFG [29:28] после сброса |

Разрядность [бит] |

|

0 |

LL |

00 |

8 |

|

0 |

LH |

01 |

16 |

|

0 |

HL |

10 |

32 |

|

1 |

xx |

10 |

32 |

|

2 |

xx |

01 |

16 |

|

3 |

xx |

00 |

8 |

3.4. Интерфейс внешней памяти

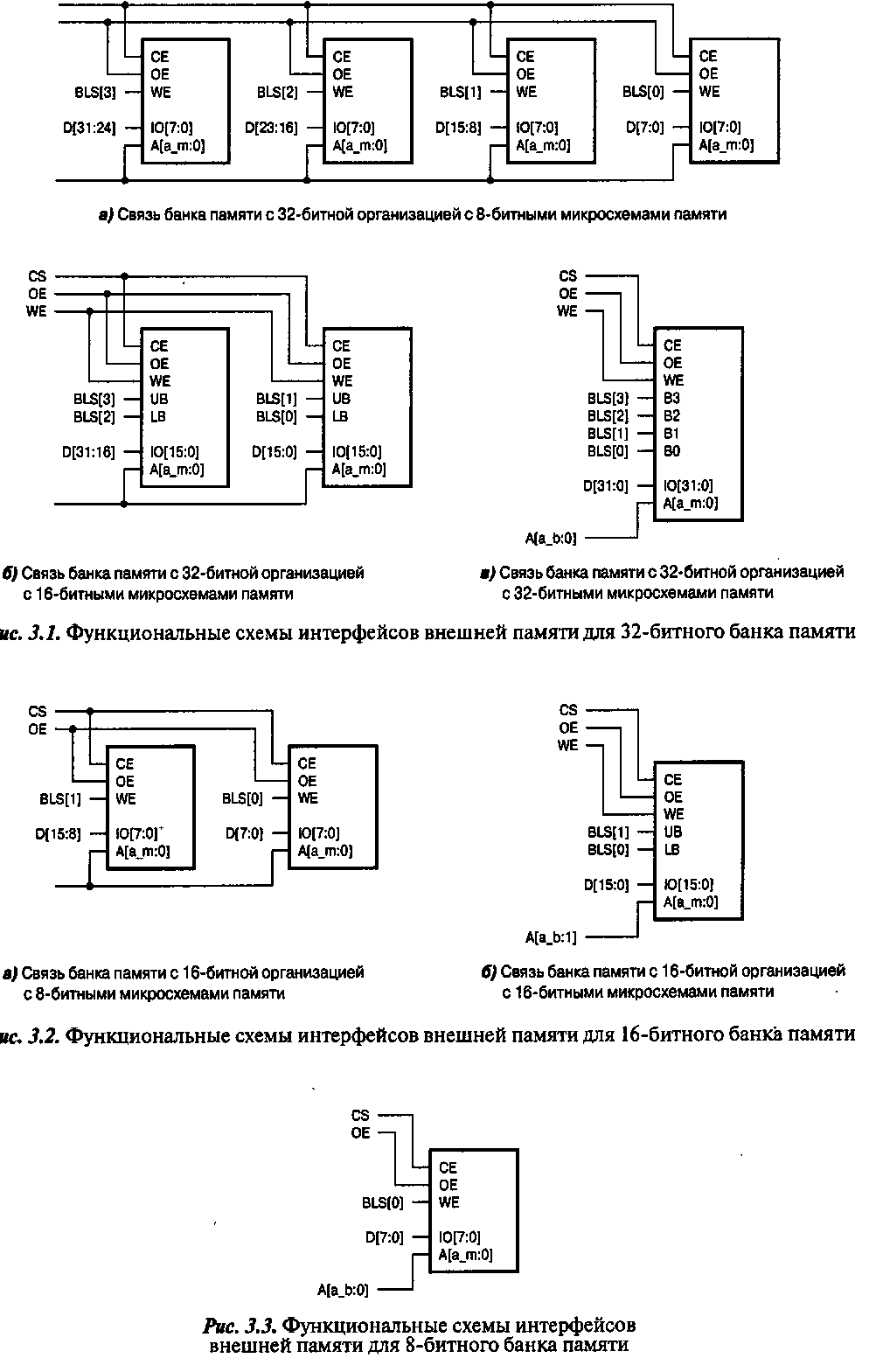

Выбор внешнего интерфейса памяти зависит от заданной организации банка (по 32, 16 или 8 битов, выбранных битами MW в регистре BCFG). Кроме того, требуется установить бит RBLE в регистре BCFG в соответствии с типом используемых устройств памяти. В случае, если внешняя память состоит из блоков по 8 бит, значение бита RBLE = 0, а для микросхем памяти, рассчитанных на работу с 16- или 32-битными данными, бит RBLE необходимо установить в 1. Если банк памяти сконфигурирован по 32 бита, то адресные линии АО и А1 могут использоваться не как линии адреса, а произвольно. Банк памяти, сконфигурированный по 16 битов, не использует адресную линию АО, а банк памяти с организацией по 8 битов требует наличия всех адресных линий до АО включительно. Конфигурирование линий А1 и/или АО как адресных или неадресных линий производится с помощью битов 23 и 24 в регистре 2 выбора функций выводов (PINSEL2). Заданная после сброса по умолчанию разрядность внешней памяти приведена в Табл. 3.5.

Функциональные схемы интерфейсов внешней памяти с 32-, 16- и 8-битной организацией приведены, соответственно, на Рис. 3.1, Рис. 3.2, Рис. 3.3. Как можно видеть из рисунков, для 32-битного банка памяти пригодны 32-, 16- и 8-битные микросхемы памяти, для 16-битного банка —16- и 8-битные микросхемы, а для 8-битного банка — только 8-битные микросхемы. Символ «а_Ь» на рисунках относится к самой старшей линии адреса в используемой шине. Символ «а_т» относится к самой старшей линии адреса в используемой микросхеме памяти.

cs ■

OE ■

A[a_b:2]

A[a_b:2]

A[a_b:1]

3.5. Типичные шинные последовательности сигналов

На Рис. 3.4 и Рис. 3.5 изображены обобщенные временные диаграммы типичных циклов обращения к внешней памяти при чтении и записи соответственно. Изображенный на рисунках сигнал XCLK — сигнал синхронизации, поступающий на микросхемы внешней памяти с вывода Р3.23 микроконтроллера. В тех случаях, когда внешняя память не задействована, этот сигнал используется, чтобы обеспечить привязку внешних устройств к тактовому сигналу микроконтроллера по времени (сигналы XCLK и CCLK имеют одинаковую частоту и различаются по фазе).

| НА ГЛАВНУЮ | | ЧТО ТАКОЕ PIC ? | | ПРОГРАММАТОР | | ПРОЕКТЫ | | СТАТЬИ | | ССЫЛКИ | | КАРТА САЙТА |