При каждом обращении к Flash-памяти в модуль МАМ из банка памяти загружается строка программного кода, состоящая из четырех 32-битных команд ARM или восьми 16-битных команд THUMB. Во время последовательного выполнения этих команд из другого банка Flash-памяти осуществляется предварительная выборка следующей по порядку строки текста программы. После выполнения последней команды в текущей 128-битной строке текста программы из банка Flash-памяти, который содержал эту строку, производится выборка очередной строки. Временные характеристики операций чтения Flash-памяти будут приведены ниже в данной главе.

Ветвления и другие изменения процесса выполнения программы вызывают перерыв в последовательном потоке вызовов команд. Ветвление (переход) назад указывает, с большой вероятностью, на наличие программного цикла. Это значит, что очередная запрошенная команда может уже содержаться в буферах

ГЛАВА 5

ветвления. В таком случае, для выполнения программы нет необходимости проводить цикл чтения Rash-памяти. При переходе вперед также существует некоторая вероятность, что новый адрес уже содержится в одном из буферов выборки с упреждением. В таком случае, и этот переход будет произведен без задержки.

Если требуется осуществить программный переход к команде, отсутствующей в одном из буферов ветвления или буферов выборки с упреждением, то необходимо произвести один цикл чтения Flash-памяти и загрузить буфера ветвления. В связи с этим, произойдет задержка выборки. При дальнейшем выполнении программы никаких задержек выборки не будет, пока в программном коде не встретится очередная подобная команда (так называемая выпадающая команда).

Контроллер Flash-памяти обнаруживает попытку доступа для чтения данных из Flash-памяти и для сохранения результатов чтения использует отдельный буфер. Способ, которым это реализуется, подобен описанному выше процессу выборки программного кода, что позволяет осуществлять более быстрый доступ к данным, если к ним обращаются последовательно. Упомянутый отдельный буфер (буфер отдельной строки), в отличие от предназначенных для доступа к программному коду буферов банков Flash-памяти, предназначен для доступа к собственно данным. При этом функция выборки с упреждением отсутствует.

5.2. Состав модуля акселератора памяти

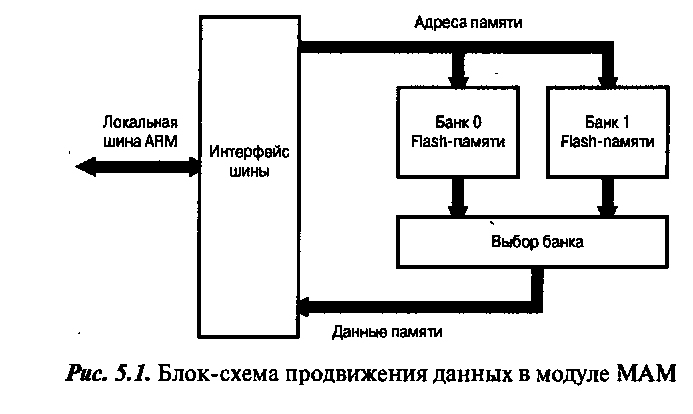

Модуль акселератора памяти состоит из нескольких функциональных блоков:

• фиксатор адреса Flash-памяти для каждого банка. Эта функция связана с банком 0 фиксации адреса;

• два банка Flash-памяти;

• фиксаторы (защелки) кода команды, фиксаторы (защелки) данных, фиксаторы (защелки) сравнения адреса;

• логические схемы ожидания.

На Рис. 5.1 изображена упрощенная блок-схема продвижения данных в модуле МАМ.

5.3. Банки Flash-памяти

В микроконтроллерах LPC2000 имеются два встроенных банка Flash-памяти, доступ к которым осуществляется параллельно и независимо. Такая структура позволяет устранить задержки при последовательном доступе к Flash-памяти.

| НА ГЛАВНУЮ | | ЧТО ТАКОЕ PIC ? | | ПРОГРАММАТОР | | ПРОЕКТЫ | | СТАТЬИ | | ССЫЛКИ | | КАРТА САЙТА |