}

break; case (2) :

I2C0NSET

NUM_byte break; default: break;

}

case (0x40): I2CONCLR = 0x04; break;

case (0x58): I2CONSET = 0x10; end_rd = 1; break; default: break;

//был передан байт данных = 0x10; //передать условие STOP I2C

//задать порядковый номер переданного байта данных = 0;

//был передан адрес ведомого + R, получен АСК //сброс флага АСС I2C, чтобы возвратить NOT АСК

//был получен байт данных, возвращен NOT АСК //передать условие STOP I2C //установить признак окончания чтения

}

0x08;

I2CONCLR = }

//функция-обработчик прерывания от TIMERO

static void Timerlnterrupt()

{

opros_kn0(); //опрос кнопки 0 opros_knl(); //опрос кнопки 1 opros_kn2(); //опрос кнопки 2 opros_kn3(); //опрос кнопки 3 static U8 old_state;

//сброс прерывания от I2C

//генерация импульсной последовательности формирования -U для питания ЖКИ if (old_state==OFF) {

OUT_U_LCD_UP; old_state=ON; }

else

//начать импульс -U ЖКИ

{

OUT_U_LCD_DOWN; old_state=OFF; }

TOIR = Oxff; }

//Инициализация и запуск TIMERO

void TIMEROinitstart()

{

//закончить импульс -U ЖКИ

//Сброс линии прерывания от Таймера О

TOTCR = О T0CCR = О T0EMR = О ТОРС = 0;

//Отключить Таймер 0 (первый бит регистра!) //Запретить все типы захвата //Запретить все типы совпадения ■ //Предделитель не делит (коэффициент деления =1)

T0MR0 = PCLK/1000; //Считать до этого значения. Выходная частота таймера // 1000 Гц

T0MCR = 3; //Сброс и прерывание от MR0 (регистр совпадения 0).

TOTCR = 1; //Включить Таймер 0 (первый бит регистра!)

}

//------------------------------------------------------------------------

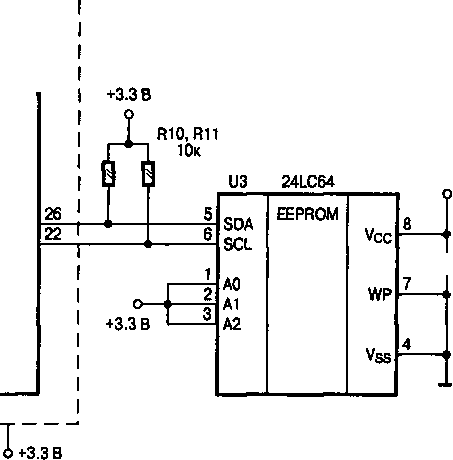

Фрагмент принципиальной схемы подключения 24LC64 к LPC2129, который необходимо добавить к базовому макету целевой пользовательской системы (Рис. 33.3), приведен на Рис. 33.6. Соединительные разъемы на схеме условно не показаны.

L

Отладочная плата LPC-H212X OUMEX

U1

LPC2129FBD64

P0.3/SDA/MAT0.0/BNT2 P0.2/SCL/CAP0.0

+3.3 в

dfi СЗ

22.0x6 В

304

Рис. 33.6. Фрагмент принципиальной схемы, добавляемый к базовому макету при подключении 24LC64 t)

Временные диаграммы записи и чтения байта I2C EEPROM 24LC64 по произвольному адресу приведены, соответственно, на Рис. 33.7а, б. Адресация ведомого устройства (микросхемы 24LC64) 7-битная, а адрес ячейки I2C EEPROM передается двумя байтами, так как микросхема имеет емкость большую, чем 256 байт. Первые четыре бита в 7-битном адресе ведомого устройства являются маской, установленной разработчиками стандарта для микросхем EEPROM 12С — 1010, а оставшиеся три бита образуют собственный адрес ведомого устройства на шине, равный 111. Этот адрес задается подачей на адресные входы 24LC64 АО, Al, А2 (Рис. 33.6) соответствующих (ВЫСОКИХ) логических уровней.

Чтобы обеспечить возможность записи и чтения по произвольным адресам, программа производит процедуру так называемой фиктивной записи — это обращение к ячейке памяти без собственно записи или чтения (указание внутренней логике микросхемы 24LC64 на ячейку для последующих записи или чтения). В случае осуществления после этой процедуры записи по произвольному адресу, ведущее устройство выдает на шину байт данных записи, дожидается от ведомого устройства подтверждения и завершает всю процедуру обмена условием STOP. Если после процедуры фиктивной записи осуществляется чтение по произвольному адресу, ведущее устройство повторно генерирует условие START, повторно выдает на шину адрес ведомого устройства (байт управления),

| НА ГЛАВНУЮ | | ЧТО ТАКОЕ PIC ? | | ПРОГРАММАТОР | | ПРОЕКТЫ | | СТАТЬИ | | ССЫЛКИ | | КАРТА САЙТА |