В общем случае, требуется два регистра совпадения, чтобы управлять одиночным перепадом на одном выходе PWM. Один регистр совпадения (PWMMR0) управляет периодом выходной последовательности PWM, сбрасывая счет при совпадении. Другой регистр совпадения управляет положением относительно начала этого периода одиночного перепада выходного сигнала PWM, задавая, таким образом, длительность выходных импульсов PWM. Для управления одиночным перепадом на одном выходе PWM может потребоваться и только один регистр совпадения, если период выходной последовательности одинаков для всех выходов PWM и, следовательно, может задаваться одним, общим для всех выходов, регистром совпадения (PWMMR0). В этом случае, сигналы на всех выходах PWM будут устанавливаться в начале каждого цикла PWM, когда происходит совпадение значения таймера со значением PWMMR0.

Чтобы управлять двумя перепадами на одном выходе PWM, требуется три регистра совпадения. Как и в предыдущем случае, регистр PWMMR0 управляет периодом выходной последовательности PWM. Другие два регистра совпадения

16.2. Структура и общее описание модуля PWM я 301

управляют положениями относительно начала периода положительного и отрицательного перепадов выходного сигнала PWM, задавая, таким образом, длительность, фазу и полярность выходных импульсов PWM. Как и в предыдущем случае, если период выходной последовательности одинаков для всех выходов PWM, то для управления двумя перепадами на одном выходе PWM требуется только два регистра совпадения. Управление двумя перепадами на одном выходе PWM позволяет формировать на этом выходе как положительные (положительный перепад предшествует отрицательному), так и отрицательные (отрицательный перепад предшествует положительному) импульсы.

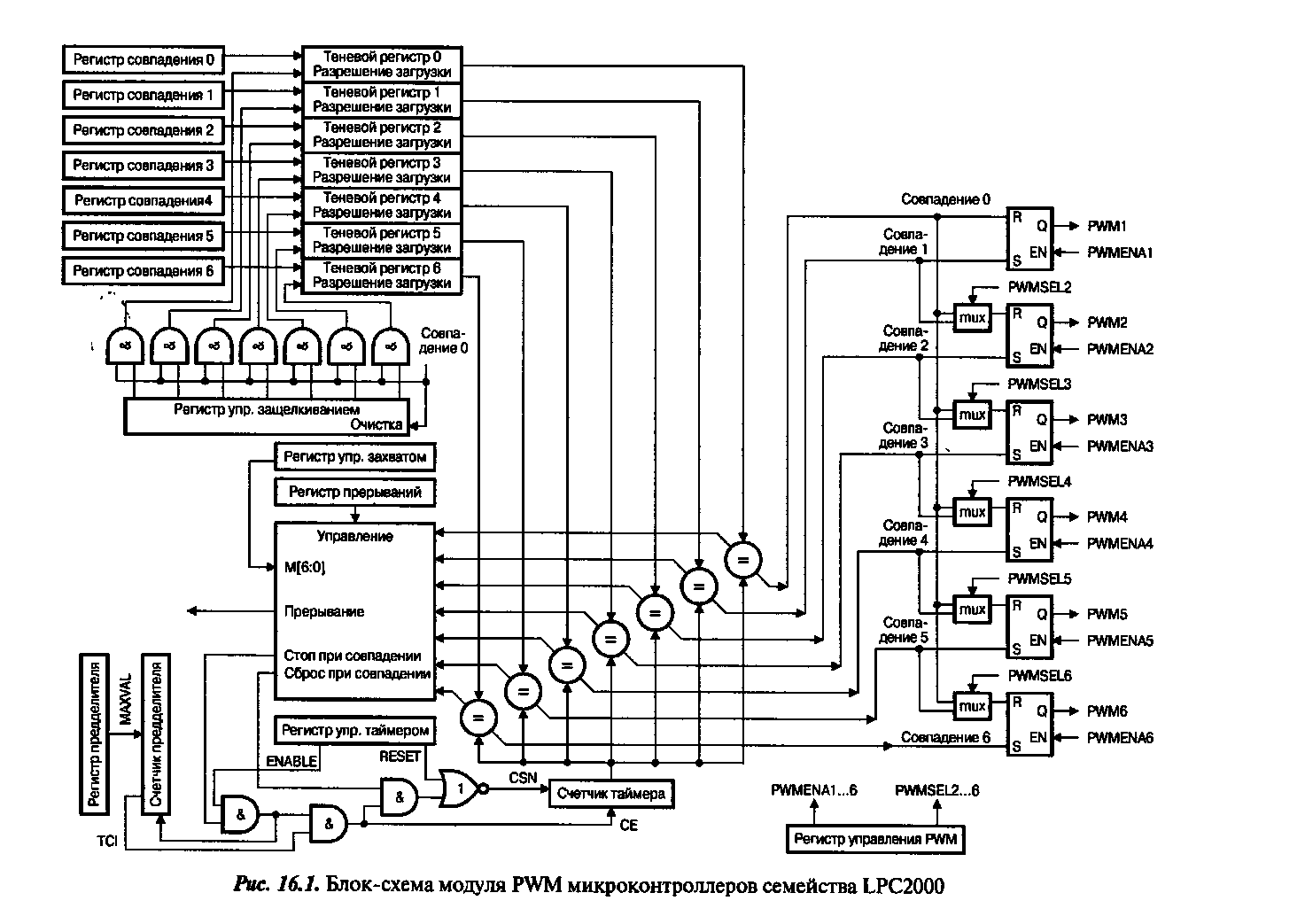

Блок-схема PWM микроконтроллеров LPC2000 приведена на Рис. 16.1. Как можно видеть из рисунка, в составе модуля PWM, по сравнению со стандартным блоком таймера (см. Рис. 15.3), имеются дополнительные узлы.

Как показано на Рис. 16.1, выбор управления одиночным или двойным перепадом выходного сигнала PWM производится мультиплексорами (mux), управляемыми битами PWMSELn.

На Рис. 16.2 изображен пример выборки выходных сигналов PWM, на котором можно проиллюстрировать взаимосвязь между значениями регистров совпадения и параметрами формируемых сигналов. Состояние отдельных выходов PWM будет циклически меняться, как изображено на рисунке, при следующих условиях:

• таймер сконфигурирован для режима PWM;

• регистр совпадения 0 сконфигурирован, чтобы сбрасывать счетчик таймера при наступлении совпадения;

• служебные биты PWMSEL2 и PWMSEL4 установлены;

• регистры совпадения PWM должны иметь следующие значения: MR0 = 100 (период выходной последовательности PWM), MR1 = 41, MR2 = 78 (для выхода PWM2),

MR3 = 53, MR4 = 27 (для выхода PWM4), MR5 = 65 (для выхода PWM5).

| НА ГЛАВНУЮ | | ЧТО ТАКОЕ PIC ? | | ПРОГРАММАТОР | | ПРОЕКТЫ | | СТАТЬИ | | ССЫЛКИ | | КАРТА САЙТА |