ГЛАВА 15

ТАЙМЕРЫ TIMERO И TIMER1

Таймеры TIMERO и TIMERl микроконтроллеров семейства LPC2000 функционально идентичны, за исключением их базовых периферийных адресов.

Таймеры TIMERO и TIMERl имеют следующие основные характеристики:

• 32-битный таймер с программируемым 32-битным предварительным делителем (предделителем);

• до четырех 32-битных каналов захвата на один таймер. Каждый из каналов захвата может захватить (скопировать) текущее значение таймера при изменении некоторого входного сигнала. В случае захвата, имеется дополнительная возможность генерировать прерывание;

• четыре 32-битных регистра сравнения (совпадения), которые позволяют:

— осуществлять непрерывное сравнение, с дополнительной возможностью генерировать прерывание при совпадении;

— остановить таймер при совпадении, с дополнительной возможностью генерировать прерывание;

— осуществлять сброс таймера при совпадении, с дополнительной возможностью генерировать прерывание;

• имеется до четырех внешних выходов, соответствующих регистрам совпадения, со следующими возможностями:

— сброс в НИЗКИЙ уровень при совпадении;

— установка в ВЫСОКИЙ уровень при совпадении;

— переключение (смена уровня, или инвертирование) при совпадении;

— при совпадении состояние выхода не изменяется.

Таймеры TIMERO и TIMERl могут использоваться для следующих приложений:

• интервальный таймер для подсчета внутренних событий микроконтроллера;

• широтно-импульсный демодулятор через входы захвата;

• независимый полнофункциональный таймер.

15.1. Общее описание

Таймер предназначен для того, чтобы подсчитывать циклы периферийной тактовой частоты (pclk) и произвольно генерировать прерывания или выполнять другие действия. Значения таймера, при достижении которых будут выполнены те или иные действия, задаются четырьмя регистрами

совпадения. Кроме того, в микроконтроллере имеются четыре входа захвата, чтобы захватить (зафиксировать) значение таймера при изменении некоторого входного сигнала, с дополнительной возможностью генерировать прерывание.

15.2. Архитектура таймера

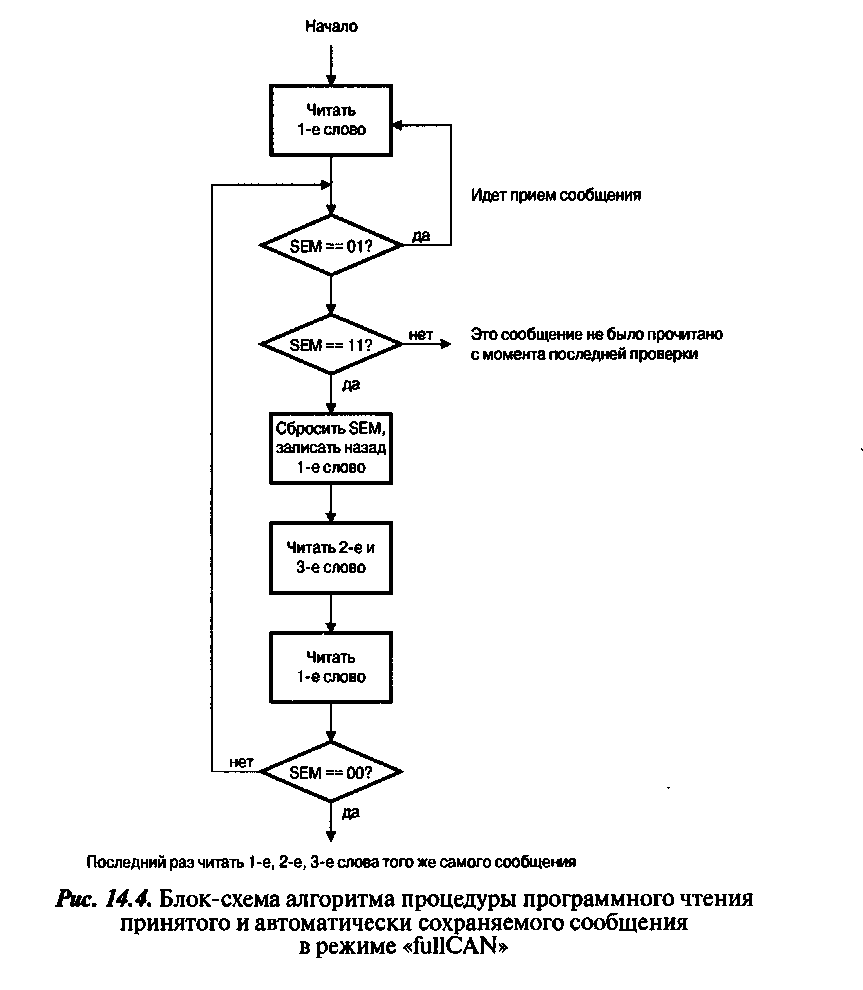

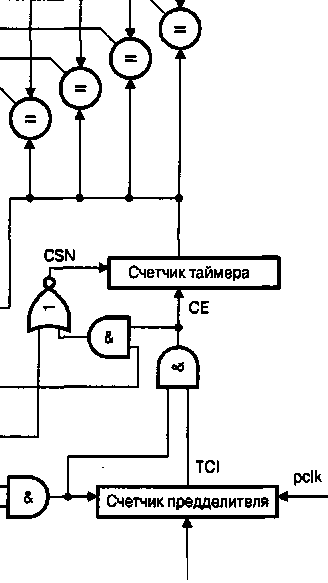

Блок-схема таймеров TIMERO и TIMERl изображена на Рис. 15.1.

Регистр совпадения 0 |~

| Регистр совпадения 1 "j—

| Регистр совпадения 2 [~

j Регистр совпадения 3

Регистр упр. совпадением

Регистр внеш. совпадения

Регистр прерываний

Управление

МАТ[3:0]

Прерывание

САР[3:0)

Стоп при совпадении Сброс при совпадении Load[3:0]

| Регистр упр. захватом "]

|

Регистр захвата 0 |

|

|

Регистр захвата 1 |

|

|

Регистр захвата 2 |

|

|

Регистр захвата З1' |

RESET | Регистр упр. таймером

ENABLE MAXVAL

| Регистр предделителя |

1> Регистр захвата 3 не может использоваться в TIMERO.

Рис. 15.1. Блок-схема TIMERO и TIMERl

15.3. Описание выводов

Краткое описание выводов микроконтроллера LPC2000, связанных с каждым таймером (на примере микроконтроллеров LPC2119/29/94 и LPC2292/94), приведено в Табл. 15.1.

| НА ГЛАВНУЮ | | ЧТО ТАКОЕ PIC ? | | ПРОГРАММАТОР | | ПРОЕКТЫ | | СТАТЬИ | | ССЫЛКИ | | КАРТА САЙТА |