ГЛАВА

13

ИНТЕРФЕЙС SPI

Интерфейс SPI микроконтроллеров LPC2000 имеет следующие особенности:

• два полнофункциональных и независимых контроллера SPI;

• интерфейс соответствует стандартной спецификации Serial Peripheral Interface (SPI);

• синхронное последовательное полнодуплексное соединение;

• интерфейс SPI поддерживает режимы ведущего и ведомого;

• максимальная задающая частота обмена составляет одну восьмую от входной тактовой частоты.

13.1. Архитектура блока SPI

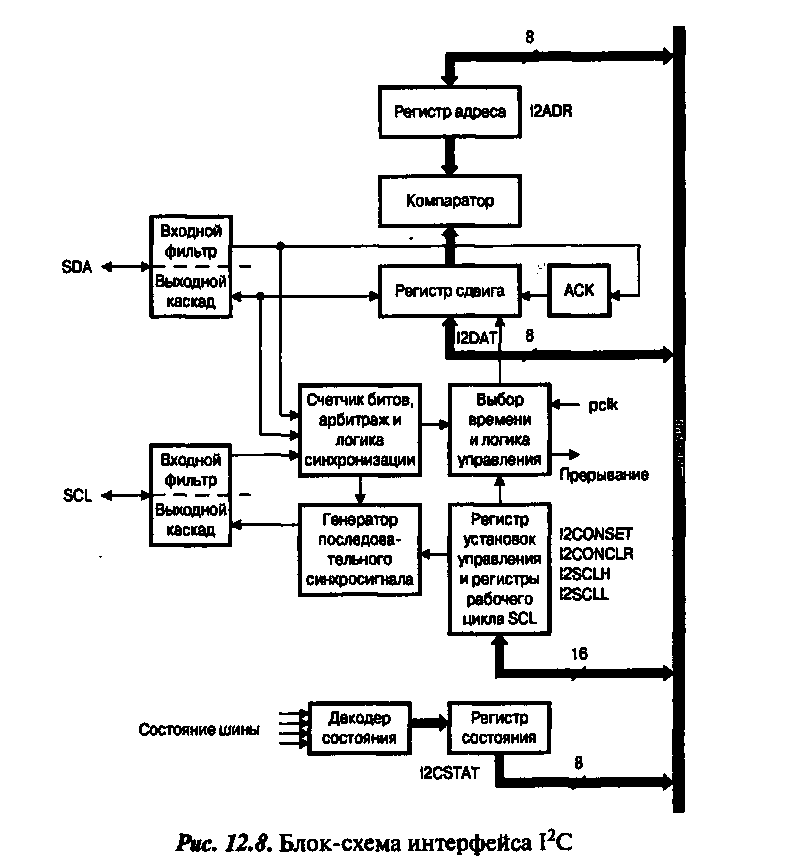

Блок-схема модуля SPI LPC2000, в соответствии с которой построены интерфейсы SPIO и SPI1, приведена на Рис. 13.1.

13.2. Описание интерфейса SPI

13.2.1. Краткий обзор SPI

Встроенные в микроконтроллеры семейства LPC2000 модули SPIO и SPI1 представляют собой полнодуплексные последовательные интерфейсы. Они могут обмениваться данными с несколькими ведущими и ведомыми устройствами SPI, подключенными к одной шине. При передаче данных через SPI, в каждый момент времени возможна связь только одного ведущего с одним ведомым. В ходе обмена данными, ведущий передает байт данных ведомому, а ведомый одновременно передает байт данных ведущему. Прием и передача тактируются одним и тем же синхросигналом SCK, который вырабатывается ведущим.

13.2.2. Передача данных через SPI

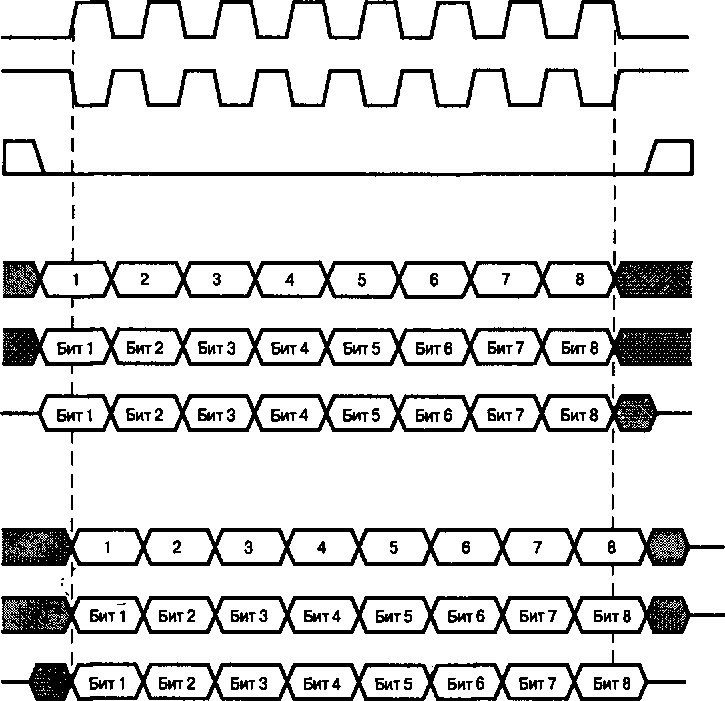

На Рис. 13.2 приведена временная диаграмма, иллюстрирующая, на примере передачи восьми битов (одного байта) данных, четыре различных формата передачи данных, которые могут использоваться в стандарте SPI. Диаграмма состоит из трех частей. В первой части показаны сигналы SSEL и SCK. Во второй части показаны сигналы MOSI и MISO, когда переменная (параметр интерфейса) СРНА = 0, а в третьей — сигналы MOSI и MISO, когда СРНА = 1.

SCK(CPOL = 0)

SCK(CPOL=1) SSEL

СРНА - О

Цикл # СРНА = О

MOSI (СРНА = 0)

MISO (СРНА = 0)

СРНА=1

Цикл # СРНА = 1

MOSI (СРНА=1)

MISO(CPHA=1)

Рис. 13.2. Возможные форматы передачи данных через SPI

Следует обратить внимание на следующие два обстоятельства. Во-первых, синхросигнал SCK будет иметь разный вид в зависимости от значения переменной CPOL, и, соответственно, сдвиг данных при передаче будет производиться по фронту или спаду сигнала SCK. Во-вторых, стандарт SPI требует, чтобы при СРНА = 1 сигнал выбора ведомого SSEL всегда переходил в неактивный (ВЫСОКИЙ) уровень между передачами отдельных байтов данных. При СРНА = О сигнал SSEL между передачами байтов может оставаться в активном (НИЗКОМ) уровне. С учетом этого, можно утверждать, что при СРНА = 0 реальная скорость обмена по шине SPI будет несколько выше, чем при СРНА = 1, за счет экономии времени, которое ведущее устройство тратит на генерацию импульса ВЫСОКОГО уровня на линии SSEL.

Необходимо заметить, что у ведущего и ведомого устройств, осуществляющих обмен через SPI, установленные комбинации переменных CPOL и СРНА должны, соответственно, совпадать.

В Табл. 13.1 приведены условия синхронизации передачи и приема данных при обмене через SPI для всех возможных комбинаций переменных CPOL и СРНА.

| НА ГЛАВНУЮ | | ЧТО ТАКОЕ PIC ? | | ПРОГРАММАТОР | | ПРОЕКТЫ | | СТАТЬИ | | ССЫЛКИ | | КАРТА САЙТА |